loading...

Let’s be honest, students these days need 35 hours in a day instead of 24. I mean, why wouldn't they?

They’re expected to balance personal life, academic hustle, skill-building, physical health, mental well-being, and, somewhere in between, all the chaos; they’re also supposed to look employable before even graduating.

A fresher today isn’t just a student; they’re expected to have internship experience, 2–3 diploma certificates, a solid LinkedIn presence, and maybe even a passion project or two. All while trying to keep their head above water.

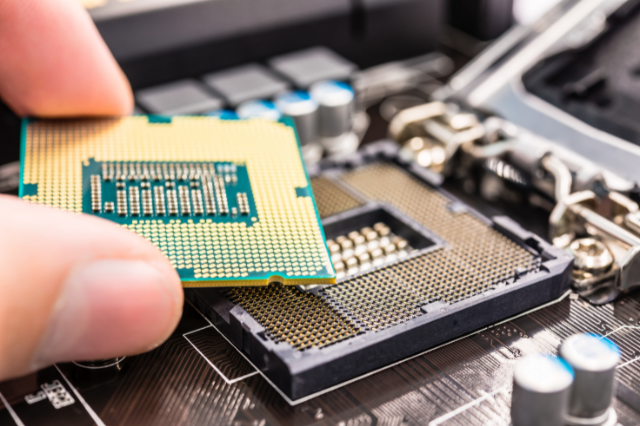

Sounds like too much to handle for anyone, let alone someone who’s 19 or 20. But that’s the reality of today’s competitive world, especially in career paths like VLSI (Very Large Scale Integration), where skill is king, and time is currency. Here’s the good news: it’s not as impossible as it sounds. Once you understand the importance of time management for engineering students, you can do it all, without burning out your blooming brain.

So here’s your practical, slightly nerdy, and real guide to the best time management tips for students preparing for VLSI careers, designed to help you not just survive, but thrive.

In VLSI design, we always start with the final functionality and work backwards to define logic and layout. Apply the same logic to your journey. Want to land a job at a semiconductor giant by the time you graduate? Work backwards. Define the skills you need: Verilog, DFT, and STA. Figure out your available months and segment your time accordingly.

This is exactly how to develop time management tips that work for your specific career goals.

Treat it like designing your life circuit, block by block.

Want to save time and get maximum output? Pick a VLSI course online that offers more than just theory. Go for something that blends training, project-based learning, and placement preparation. That’s one of the best time management tips you'll ever apply: combine efforts in one place.

Look for a VLSI online course with a certificate that teaches industry tools like Synopsys and Cadence, lets you build real projects, and offers internship exposure. The time you save switching between disconnected resources can be invested in skill enhancement and soft skill polishing.

Creating a to-do list is easy. But real productivity? That comes from time blocking. Instead of simply writing “Study Verilog,” block 4–6 PM, specifically for Verilog labs or simulation practice. Allocate time for focused tasks—tool sessions, mock interviews, and even breaks.

This technique, one of the best time management tips for students, minimizes distractions and helps you get into deep work mode faster. Whether you're enrolled in a VLSI online course with a certificate or juggling college assignments, blocking your hours is your secret weapon.

Being brilliant at timing diagrams is great, but if you can’t explain your thought process or write an impactful resume, it’s a problem. Smart engineers divide time intentionally: 60% on core concepts and 40% on things like GitHub, LinkedIn, presentations, and networking.

Why is this one of the best time management tips? Soft skills are increasingly part of what makes engineers employable. Whether you’re in a VLSI course online or prepping independently, make time for it all.

Binge-watching Suits after a long study session might seem like a well-earned break, but it often leads to burnout. Enter the Pomodoro method: 25 minutes of focused learning, followed by a 5-minute break.

For VLSI students especially, this keeps your attention span sharp and your brain in debug mode. It’s one of the best time management tips you’ll wish you knew earlier.

Let’s be real, you’re not a machine. Use tech to save time. Set reminders using Google Calendar, track habits with Notion, and monitor your screen time. Automating small routines gives you more bandwidth to focus on debugging your Verilog code or improving a schematic layout.

If you're pursuing a VLSI online course with a certificate, these tools can help keep your deadlines and submissions on track without constant mental strain.

Notion, Trello, Pomodoro, Bullet Journals—there are too many options, and switching between all of them is a time sink. The real hack? Pick one, make it yours, and stick with it.

This is crucial when you're managing a demanding curriculum or a VLSI course online that includes both tool training and project deadlines. Simplicity saves brainpower.

This one’s harsh but true. Whether it's your first internship, your capstone project, or your first VLSI online course with a certificate, you’ll never feel 100% ready. That’s okay. Start anyway.

Time management isn’t about perfection; it’s about action. In engineering and in life, progress is iterative. You debug, you improve, you evolve. The sooner you start, the faster you grow.

The importance of time management for engineering students, especially those chasing a career in chip design, cannot be overstated. VLSI is intense, dynamic, and skill-driven. You don’t just need textbook smarts; you need strategic planning, consistent upskilling, and daily execution.

When you start implementing these best time management tips, you realize it’s not about doing more but about doing things smarter. Just like chip layout optimization, it's about working with limited space (or time) to achieve maximum output.

So plan like a designer, execute like a coder, and grow like a silicon wafer in a cleanroom. If you're serious about VLSI, there’s never been a better time to start managing your hours like a pro—with a VLSI course online that fits your pace and goals.

Your career in VLSI? It’s already ticking. Make every second count.

A to Z on India, Japan & the Future of Semiconductor Industry: A New Chapter in Tech Collaboration

A to Z on India, Japan & the Future of Semiconductor Industry: A New Chapter in Tech Collaboration

RTL Design vs Physical Design: What's the Real Difference?

RTL Design vs Physical Design: What's the Real Difference?

The Future of the Semiconductor Industry: What Indian Students Should Know

The Future of the Semiconductor Industry: What Indian Students Should Know

Top 7 Career Paths After Completing a VLSI Course

Top 7 Career Paths After Completing a VLSI Course

Best Time Management Tips for Students Preparing for VLSI Careers

Best Time Management Tips for Students Preparing for VLSI Careers

Mastering VLSI Physical Design: A Comprehensive Course Overview

Mastering VLSI Physical Design: A Comprehensive Course Overview

The Complete FPGA and ASIC Guide

The Complete FPGA and ASIC Guide

Verilog Essentials: Mastering the Fundamentals of Hardware Description Language

Verilog Essentials: Mastering the Fundamentals of Hardware Description Language

Unleashing the Power of System Verilog: A Comprehensive Guide for Aspiring Designers

Unleashing the Power of System Verilog: A Comprehensive Guide for Aspiring Designers

Demystifying VLSI chip Design: Exploring the Core Concepts of VLSI Courses

Demystifying VLSI chip Design: Exploring the Core Concepts of VLSI Courses

Basics of VLSI - An Ultimate Guide

Basics of VLSI - An Ultimate Guide

Career Prospects After Completing A VLSI Course

Career Prospects After Completing A VLSI Course

Top 5 Reasons To Take Up A Professional VLSI Course

Top 5 Reasons To Take Up A Professional VLSI Course

Mastering VLSI Design: A Comprehensive Guide To Understanding Complex Integrated Circuits

Mastering VLSI Design: A Comprehensive Guide To Understanding Complex Integrated Circuits

Future-Proof Your Career With A VLSI Course: How Learning About Integrated Circuits Can Boost Your Job Prospects?

Future-Proof Your Career With A VLSI Course: How Learning About Integrated Circuits Can Boost Your Job Prospects?

System Verilog: An Overview

System Verilog: An Overview

Introduction to Hardware Description Language (HDL)

Introduction to Hardware Description Language (HDL)

Unlock The Potential Of VLSI Design With An Integrated VLSI Course Online

Unlock The Potential Of VLSI Design With An Integrated VLSI Course Online

Universal Verification Methodology:An Efficient Verification Approach

Universal Verification Methodology:An Efficient Verification Approach

How to Write a Verilog Module for Design and Testbench

How to Write a Verilog Module for Design and Testbench